FFT and multirate filter banks and wavelets designed by students with only basic logic experience. We discuss the required background knowledge, key target smart firmware for FPGAs and possible advanced designs, e.g. Xilinx is widely used in both industries and academics.Intel erstwhile Altera are especially meant for academicians,at whole Xilinx are ahead of Altera. We have evaluated the Altera/Simulink tool flow used for a University design environment and present design experience of a semester course at FAMU-FSU College of Engineering.

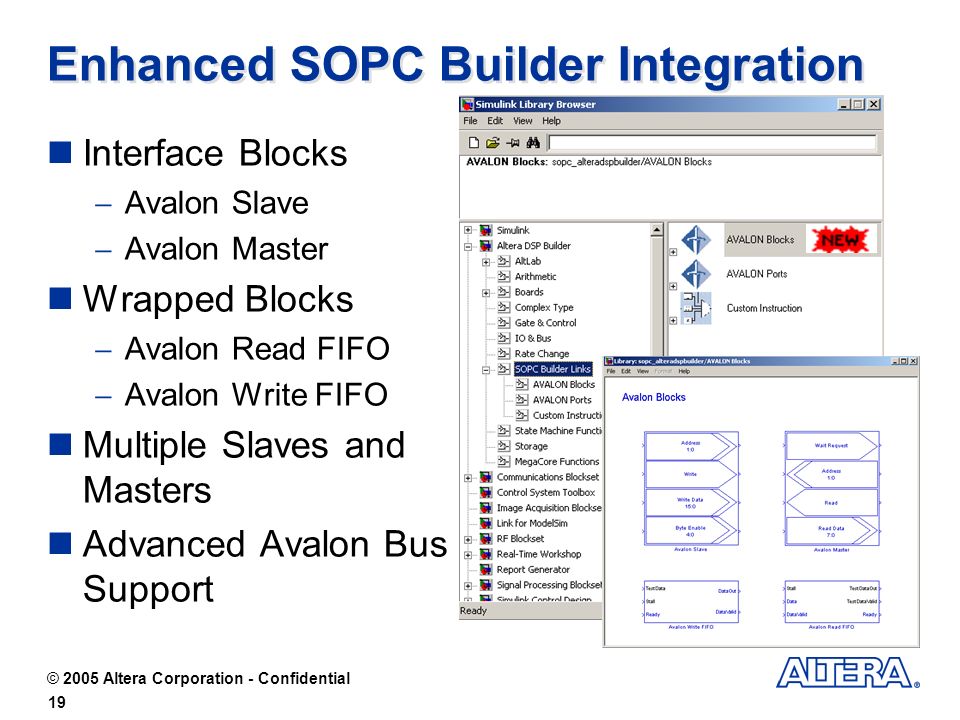

This not only allows the over 1 million MatLab users to design with FPGAs but also to by-pass the hardware design engineer and leads therefore to shorter development time. There are two really important things to note here. In this case, Stratix 10 FPGAs and SoCs will be able to offer DSP datapaths providing up to 10TFLOPS of single-precision floating-point. I am using XESS board (XST-3000) board which has a onboard video decoder chip available. Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type. The requirement of short time-to-market, however, requires to replace the traditional HDL based designs by a MatLab/Simulink-based design flow. These hardened floating-point DSP blocks are also going to be available in Altera’s 14nm Stratix 10 FPGAs and SoCs when they become available in 2015. I suggest you to use Altera DSP Builder, it is a good tool to start to doing a model, simulate and implement to the FPGA. I am new in altera i am using Simulink matrix block as input to the altera blocksets design but data incompatibility problem arises plz someone.

Perry, R.ĭesign of current DSP applications using state-of-the art multi-million gates devices requires a broad foundation of engineering skills ranging from knowledge of hardware-efficient DSP algorithms to CAD design tools. Smart Altera firmware for DSP with FPGAs Smart Altera firmware for DSP with FPGAs

0 kommentar(er)

0 kommentar(er)